Difference between revisions of "Papilio 500K"

(Created page with "== Introduction == == Features == == Application Ideas == == Cautions == == Schematic == == Specification == == Pin definition and Rating ...") |

(→How to buy) |

||

| (2 intermediate revisions by one other user not shown) | |||

| Line 1: | Line 1: | ||

== Introduction == | == Introduction == | ||

| + | The Papilio One 500K comes fully assembled with a Xilinx XC3S500E and 4Mbit SPI Flash memory. | ||

| + | Papilio is an open-source [http://en.wikipedia.org/wiki/Fpga FPGA] project intended for education, hobbyists, engineers, or anyone interested in learning [http://papilio.cc/index.php?n=Papilio.DigitalElectronics Digital Electronics] in a friendly community. | ||

| − | + | [[File:papilione.jpg]] | |

| − | |||

== Features == | == Features == | ||

| Line 18: | Line 19: | ||

== Cautions == | == Cautions == | ||

| − | + | The Papilio One does not ship with the headers populated in order to allow the end user the greatest flexibility in deciding the final configuration. Headers can be ordered along with the Papilio One. | |

| − | + | The recommended configuration is to use Female Headers on the Papilio One's Wing Sockets and to use Male Headers on the Wings. | |

| − | |||

| − | |||

== Schematic == | == Schematic == | ||

| Line 30: | Line 29: | ||

== Specification == | == Specification == | ||

| + | === Power === | ||

| + | *Four independent power rails at 5V, 3.3V, 2.5V, and 1.2V. | ||

| + | *Power supplied by a power connector or USB. | ||

| + | === USB === | ||

| + | *Two channel USB connection for JTAG and serial communications implemented with FT2232. | ||

| + | *EEPROM memory to store configuration settings for FT2232 USB chip. | ||

| + | === Spartan 3E FPGA === | ||

| + | *32MHz oscillator that can be used by Xilinx's DCM to generate any required clock speed. | ||

| + | *VTQFP-100 footprint that supports Xilinx XC3S100E, XC3S250E, and XC3S500E parts. | ||

| + | *Bank 0-3 can be jumpered to support 1.2V, 2.5V, or 3.3V. | ||

| + | *Xilinx JTAG header supports Xilinx JTAG cables. | ||

| + | *Power and I/O are routed to the side headers. | ||

| + | *Board can be used with Bread Boards if only the outside row of the side headers is populated. | ||

| − | + | === Wings === | |

| − | + | *Easily add new functionality to the Papilio One with Wings that snap onto the board. | |

| + | *48 bidirectional I/O lines which can be split up as: | ||

| + | *#1 - 32 Bit Wing or | ||

| + | *#3 - 16 Bit Wings or | ||

| + | *#6 - 8 Bit Wings | ||

| + | |||

== Pin definition and Rating == | == Pin definition and Rating == | ||

| Line 79: | Line 96: | ||

== How to buy == | == How to buy == | ||

| − | + | Here to buy Pailio 500K on [http://store.linksprite.com/papilio-one-500k/ store] | |

| − | |||

| − | |||

| − | |||

== See Also == | == See Also == | ||

Latest revision as of 00:54, 19 February 2014

Contents

Introduction

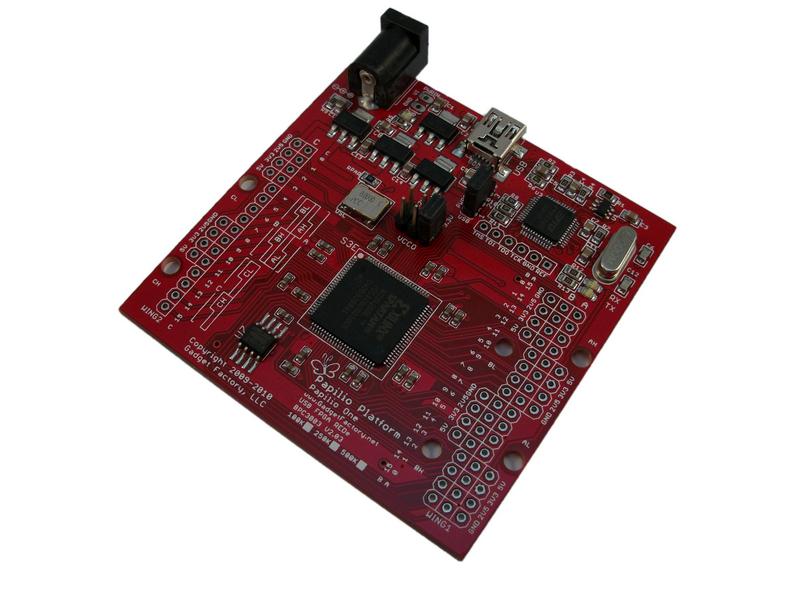

The Papilio One 500K comes fully assembled with a Xilinx XC3S500E and 4Mbit SPI Flash memory.

Papilio is an open-source FPGA project intended for education, hobbyists, engineers, or anyone interested in learning Digital Electronics in a friendly community.

Features

Application Ideas

Cautions

The Papilio One does not ship with the headers populated in order to allow the end user the greatest flexibility in deciding the final configuration. Headers can be ordered along with the Papilio One. The recommended configuration is to use Female Headers on the Papilio One's Wing Sockets and to use Male Headers on the Wings.

Schematic

Specification

Power

- Four independent power rails at 5V, 3.3V, 2.5V, and 1.2V.

- Power supplied by a power connector or USB.

USB

- Two channel USB connection for JTAG and serial communications implemented with FT2232.

- EEPROM memory to store configuration settings for FT2232 USB chip.

Spartan 3E FPGA

- 32MHz oscillator that can be used by Xilinx's DCM to generate any required clock speed.

- VTQFP-100 footprint that supports Xilinx XC3S100E, XC3S250E, and XC3S500E parts.

- Bank 0-3 can be jumpered to support 1.2V, 2.5V, or 3.3V.

- Xilinx JTAG header supports Xilinx JTAG cables.

- Power and I/O are routed to the side headers.

- Board can be used with Bread Boards if only the outside row of the side headers is populated.

Wings

- Easily add new functionality to the Papilio One with Wings that snap onto the board.

- 48 bidirectional I/O lines which can be split up as:

- 1 - 32 Bit Wing or

- 3 - 16 Bit Wings or

- 6 - 8 Bit Wings

Pin definition and Rating

Mechanic Dimensions

Usage

Hardware Installation

Programming

FAQ

Please list your question here:

Support

If you have questions or other better design ideas, you can go to our forum to discuss or creat a ticket for your issue at linksprite support.

Resources

How to buy

Here to buy Pailio 500K on store

See Also

Other related products and resources.

Licensing

This documentation is licensed under the Creative Commons Attribution-ShareAlike License 3.0 Source code and libraries are licensed under GPL/LGPL, see source code files for details.